Kiểm chứng tốc độ thay đổi điện áp (dV/dt) trong bộ truyền động động cơ

23/09/2025 16:57 Số lượt xem: 9Kiểm chứng tốc độ thay đổi điện áp (dV/dt) trong bộ truyền động động cơ có thể áp dụng trong quá trình phát triển trong phòng thí nghiệm cũng như trực tiếp trên ứng dụng cuối cùng với khách hàng tại hiện trường.

Độ dốc biên của bộ nghịch lưu có thể thử nghiệm nhanh chóng và thực tế bằng máy hiện sóng mà không cần phải đánh giá thủ công từng biên riêng lẻ trong miền thời gian. Việc xác thực dV/dt trong bộ truyền động động cơ có thể áp dụng trong quá trình phát triển ở phòng thí nghiệm cũng như trực tiếp trên ứng dụng cuối cùng với khách hàng ngoài hiện trường.

Tại sao xác thực dV/dt lại quan trọng?

Nếu độ dốc biên của điện áp một pha động cơ (gọi là dV/dt) quá lớn, nó có thể gây hư hại cho các cuộn dây thông qua hiện tượng phóng điện cục bộ trong các cuộn dây của động cơ. Một giá trị giới hạn sử dụng rộng rãi trong ngành là 5kV/μs, cần tuân thủ và kiểm tra nhằm bảo vệ động cơ. Mặc dù việc kiểm tra này thường thực hiện trong giai đoạn phát triển bằng các thử nghiệm xung kép trong phòng thí nghiệm, nhưng bài viết này tập trung vào việc thử nghiệm ứng dụng thực tế trong điều kiện vận hành thật.

.jpg)

Nếu độ dốc biên của điện áp một pha động cơ quá lớn, nó có thể gây hư hại cho cuộn dây (Ảnh st)

Điều quan trọng cần hiểu là trong một chu kỳ dòng điện pha có rất nhiều biên dạng khác nhau. Ở tần số dòng điện pha 50Hz và tần số chuyển mạch 2kHz, có 80 biên dạng khác nhau, bao gồm 40 biên dương và 40 biên âm. Ở tần số 16kHz, đã có tới 640 biên dạng cần phải đánh giá cho mỗi điều kiện tải. Do đó, cần có một phương pháp đo lường nhanh chóng, vì việc đánh giá thủ công từng biên dạng riêng lẻ trong miền thời gian sẽ quá mất thời gian.

Độ dốc của các biên và sự phân bố của chúng trong chu kỳ dòng điện pha chủ yếu phụ thuộc vào các linh kiện bán dẫn công suất và điện trở cổng của chúng. Nhiều yếu tố ảnh hưởng thứ cấp bổ sung khác bao gồm phụ tải của động cơ, các quá trình quá độ trong thời gian chết (chuyển mạch mềm), chiều của dòng điện pha, biên độ của dòng điện pha, hệ số công suất, loại điều chế độ rộng xung (PWM), độ sắc nét của diode, loại và chiều dài cáp, nhiệt độ của các linh kiện bán dẫn, cũng như bố trí mạch in và mođun công suất.

Xác định dV/dt như thế nào?

Máy hiện sóng có thể ghi lại hai tham số sau đây:

a) Dòng điện pha

b) Điện áp pha chuyển mạch

.jpg)

Hình 1. Phác thảo các điểm đo điện áp pha và dòng điện pha (Ảnh st)

Kênh toán học của máy hiện sóng sau đó sẽ vi phân và chuẩn hóa điện áp pha chuyển mạch. Việc vi phân sẽ biến đổi độ dốc biên từ miền thời gian sang miền biên độ. Việc chuẩn hóa giúp đưa kết quả về đơn vị kV/μs.

Việc biến đổi sang miền biên độ có ưu điểm là có thể đọc trực tiếp kết quả trên trục y. Do đó, không cần phải vất vả đánh giá từng cạnh trong miền thời gian nữa.

Nên chọn chu kỳ đo sao cho hiển thị chính xác một chu kỳ hoàn chỉnh của dòng điện pha trên máy hiện sóng. Điều này có nghĩa là có thể ghi lại và hiển thị tất cả các biên của một trạng thái vận hành cụ thể chỉ trong một lần đo duy nhất.

Đánh giá kết quả đo

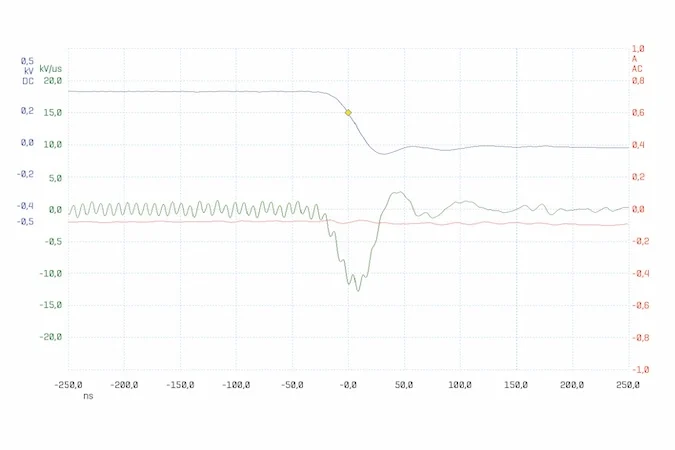

Có thể đọc dV/dt trực tiếp từ kênh toán học. Có thể thấy ngay là tất cả các cạnh của chu kỳ đều nằm trong giới hạn đã đặt hay các giá trị giới hạn đã bị vượt quá (các điểm nhọn màu xanh lá cây trong Hình 2).

.jpg)

.jpg)

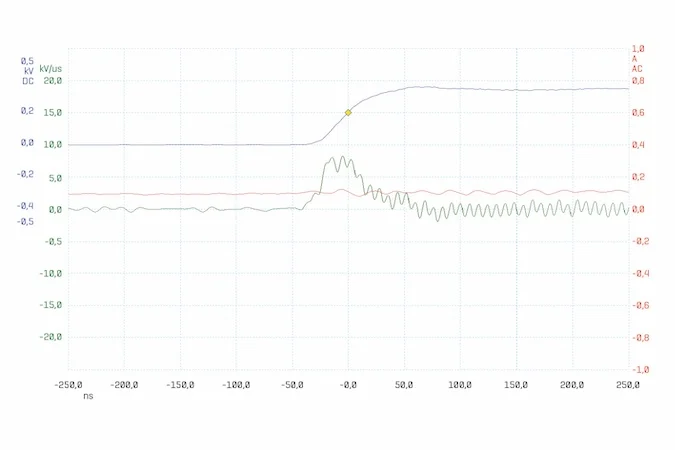

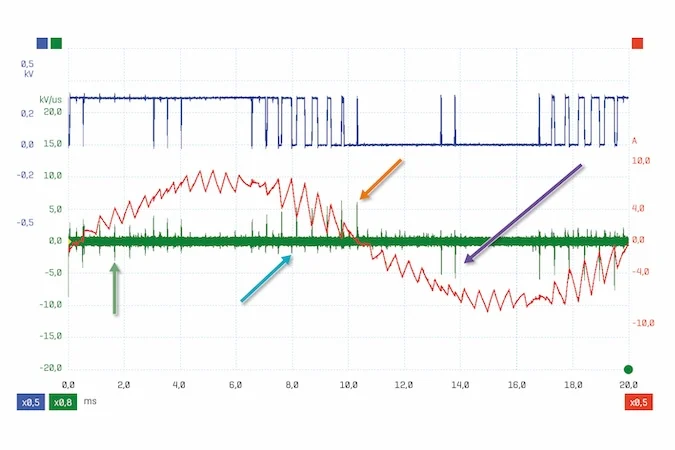

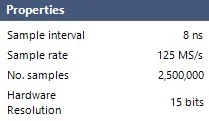

Hình 2. Đo dV/dt (động cơ không đồng bộ ba pha 2,2kW, không tải) (Ảnh st)

CH1 = Điện áp pha so với DC

Ch2 = Dòng điện pha

MC = dV/dt

Nếu lấy giá trị giới hạn 5kV/μs làm giá trị tham chiếu trong ví dụ trên, ta có thể thấy ngay rằng giá trị giới hạn này đã bị vượt quá đáng kể, ngoại trừ trong vùng cắt qua điểm 0 của dòng điện pha.

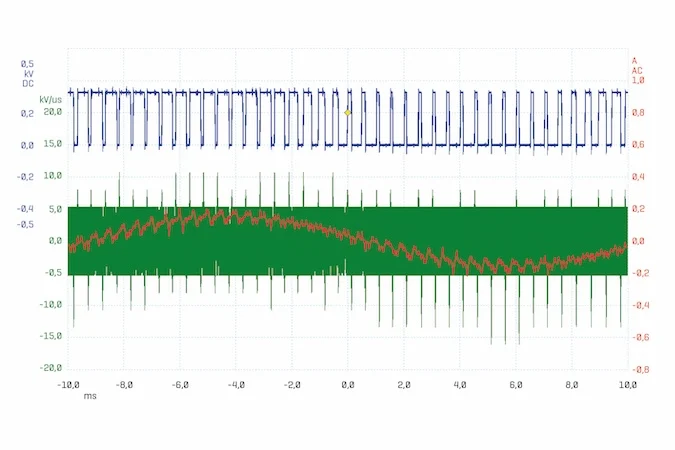

Các Hình 3 và 4 cho thấy các bức ảnh chụp cận cảnh của một biên (a) đang giảm và (b) đang tăng. Bạn có thể thấy rõ cách tính toán dV/dt ánh xạ biên thực.

Hình 3. Biên giảm (xem chi tiết ở hình dưới) (Động cơ không đồng bộ ba pha 90W, không tải) (Ảnh st)

Ch1 = Điện áp pha so với DC

Ch2 = Dòng điện pha

MC = dV/dt

Hình 4. Biên tăng (xem chi tiết ở hình dưới) (Động cơ không đồng bộ ba pha 90W, không tải) (Ảnh st)

CH1 = Điện áp pha so với DC

Ch2 = Dòng điện pha

MC = dV/dt

Phân công Biên/IGBT

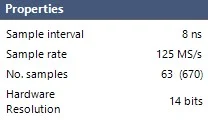

Cần phải tối ưu hóa nếu độ dốc biên quá cao. Trong trường hợp đơn giản nhất, có thể điều chỉnh điện trở cổng. Để tối ưu hóa, mọi cạnh quá dốc phải gán cho IGBT (transistor lưỡng cực cổng cách điện) chịu trách nhiệm và hướng chuyển mạch của nó. Nói một cách đơn giản: Bạn phải biết IGBT HS (phía cao) hay LS (phía thấp) chịu trách nhiệm và liệu nó hiện đang bật hay tắt. Việc gán yêu cầu phân biệt trường hợp đối với (a) hướng của dòng điện pha và (b) hướng của dV/dt.

Bảng sau đây liệt kê nhiệm vụ đúng:

Bảng 1. Bảng phân công IGBT chịu trách nhiệm cho biên.

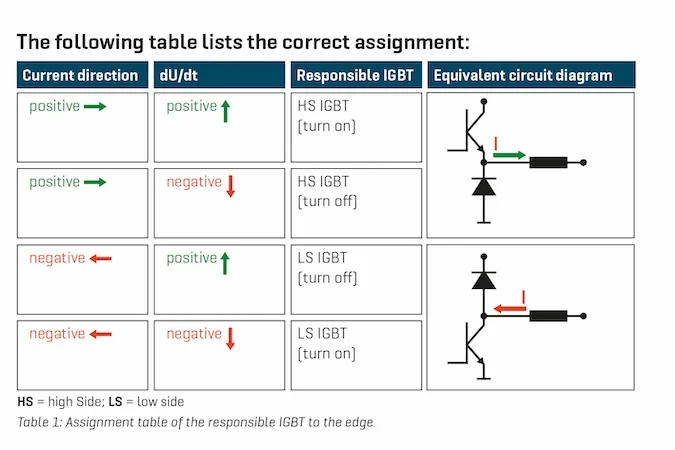

Hình 5 minh họa nội dung của bảng trên dưới dạng đồ họa.

Hình 5. Biểu diễn đồ họa: Phân công IGBT chịu trách nhiệm cho biên tương ứng (Ảnh st)

Hình 6 minh họa việc chỉ định IGBT của bộ nghịch lưu chuyển mạch PWM đầu phẳng.

Hình 6. Đo dV/dt (động cơ không đồng bộ ba pha 2,2kW, PWM đầu phẳng, có tải) (Ảnh st)

Ch1 = Điện áp pha so với DC

Ch2 = Dòng điện pha

MC = dV/dt

Mũi tên màu cam: dV/dt = dương & dòng điện pha = dương => Bật HS IGBT

Mũi tên màu tím: dV/dt = âm & dòng điện pha = âm => Bật LS IGBT

Mũi tên màu ngọc lam: dV/dt = dòng điện âm & pha = dương => Tắt HS IGBT

Mũi tên xanh: Không có biên; nghĩa là, đây là liên kết điện dung có biên dốc từ pha lân cận.

Lưu ý: Với các biên nhanh và ghép nối điện dung cao giữa các pha động cơ, hiện tượng nhiễu xuyên âm xảy ra. Những hiện tượng này có thể nhìn thấy thông qua các xung dốc trên điện áp pha và do đó, cũng có thể đánh giá bằng phương pháp đã trình bày ở đây. Tuy nhiên, điều này không quan trọng vì theo lý do vật lý, hiện tượng nhiễu xuyên âm không thể dốc hơn các biên. Nếu nghi ngờ, việc phóng to phép đo sẽ cung cấp thông tin về việc đó là biên hay hiện tượng nhiễu xuyên âm.

Ghi chú về sơ đồ mạch tương đương trong Bảng 1

Vẽ sơ đồ mạch tương đương cho nửa cầu của một pha có thể đơn giản hóa lời giải thích về hành vi chuyển mạch vì mọi sơ đồ mạch tương đương chỉ chứa một IGBT hoạt động. Nửa cầu của một pha hoạt động như một giai đoạn BUCK (chế độ giảm áp) nếu dòng điện pha dương và như một giai đoạn BOOST (chế độ tăng áp) nếu dòng điện pha âm. Do đó, nửa cầu của một pha có thể chia thành hai sơ đồ mạch tương đương, cụ thể là thành (a) giai đoạn buck và (b) giai đoạn boost. Khi làm như vậy, diode mô phỏng diode song song ngược của IGBT đối diện, luôn dẫn điện trong thời gian chết. (Điều kiện tiên quyết: hoạt động không có khe hở, gần như luôn có trong hoạt động của bộ nghịch lưu).

Cải thiện chất lượng đo

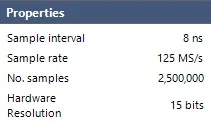

Để đạt kết quả tốt cần phải vượt qua một số trở ngại vì chất lượng và độ chính xác của dV/dt được tính toán phụ thuộc rất nhiều vào nhiễu của kênh toán học. Nó xảy ra trong quá trình tính toán và không phải là nhiễu tín hiệu!

Để có kết quả phù hợp, nhiễu phải nhỏ hơn đáng kể so với dV/dt của các biên chuyển mạch (tỷ lệ tín hiệu trên tiếng ồn). Do đó, điều quan trọng là phải biết nhiễu đến từ đâu và làm thế nào để giữ nó ở mức tối thiểu.

Hình 7. Biểu diễn khái niệm về nhiễu (Ảnh st)

Lưu ý: Có thể giảm nhiễu bằng (a) độ phân giải AD theo chiều dọc cao hơn, (b) phạm vi đo nhỏ nhất có thể và (c) tốc độ lấy mẫu thấp hơn.

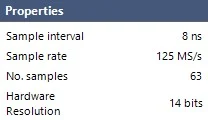

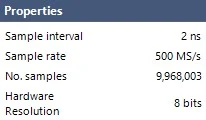

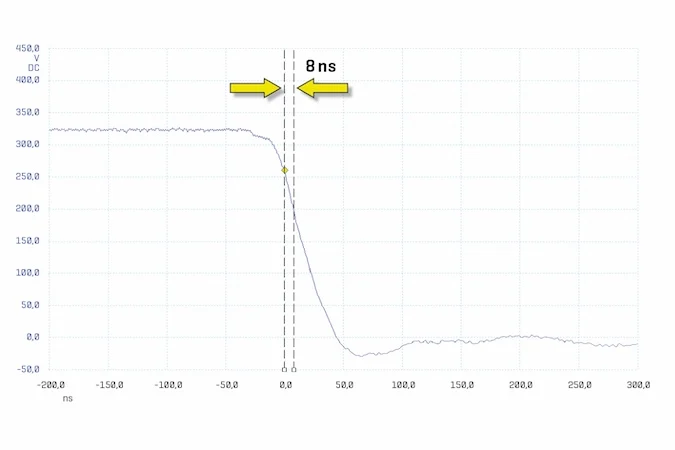

So sánh sau đây minh họa cách độ phân giải AD cao hơn và thời gian lấy mẫu dài hơn giúp làm giảm nhiễu. Người ta đã so sánh các thiết lập đo sau đây:

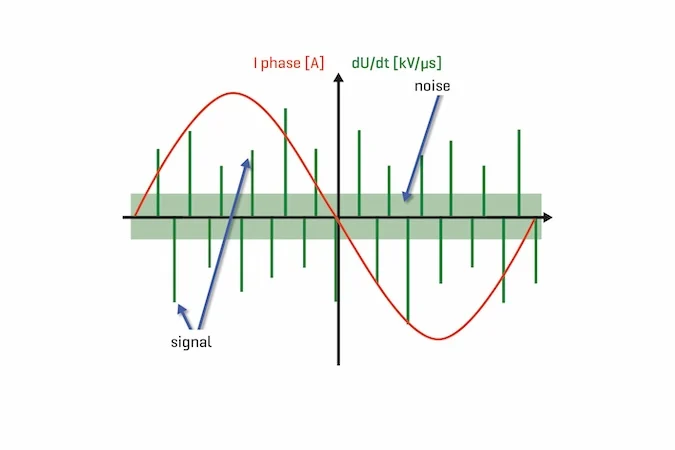

a) Độ phân giải AD 15-Bit/thời gian lấy mẫu 8 nano giây (ns) (Hình 8)

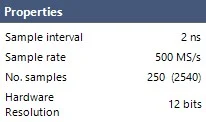

b) Độ phân giải AD 8-Bit/thời gian lấy mẫu 2ns (Hình 9)

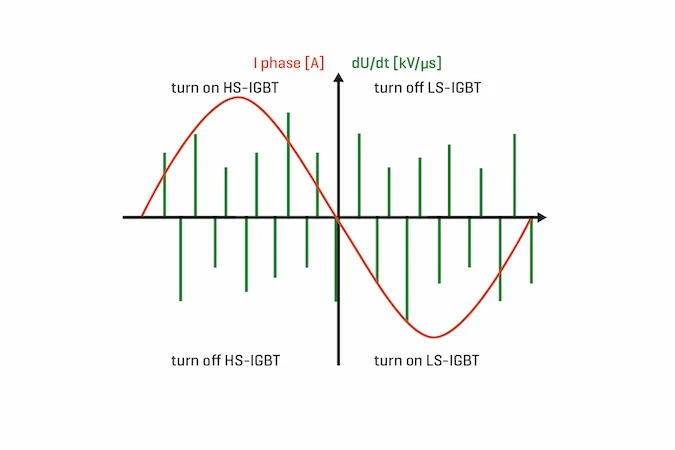

Hình 8 cho thấy độ phân giải AD cao (15bit) và thời gian lấy mẫu dài (8ns) tạo ra độ nhiễu thấp.

Hình 8. Độ nhiễu thấp với tham số 15-bit/8ns (Ảnh st)

CH1 = Điện áp pha so với DC

Ch2 = Dòng điện pha (đã lọc)

MC = dV/dt

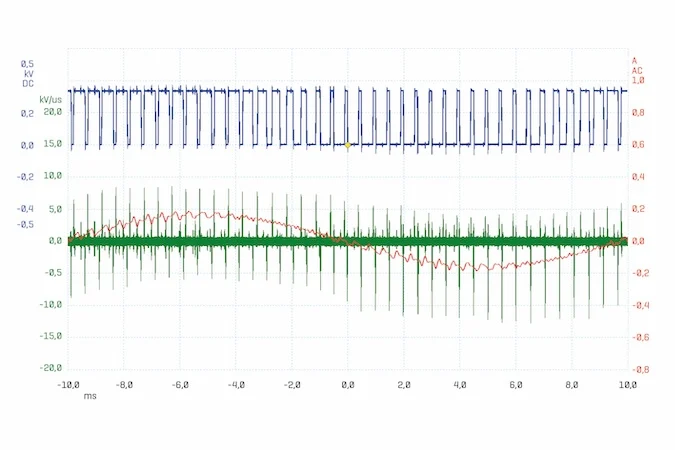

Hình 9 cho thấy độ phân giải AD thấp (8bit) và thời gian lấy mẫu ngắn (2ns) dẫn đến nhiễu cao.

Sự khác biệt về nhiễu có thể thấy rõ. Trong Hình 9, nhiễu thậm chí còn cao hơn giá trị giới hạn thường dùng (>5kV/μs) và do đó không thể sử dụng cho phép đo giá trị giới hạn này.

Hình 9. Độ nhiễu cao với tham số 8-bit/2ns (Ảnh st)

Ch1 = Điện áp pha so với DC

Ch2 = Dòng điện pha (đã lọc)

MC = dV/dt

Nhiễu trong kênh toán học đến từ đâu?

Nguyên nhân chủ yếu là nhiễu lượng tử hóa của bộ chuyển đổi AD của máy hiện sóng. Nó gây ra lỗi biên độ tần số cao, dẫn đến lỗi dV/dt trong quá trình phân biệt trong kênh toán học. Nhiễu trong kênh toán học là chuỗi của tất cả các lỗi dV/dt và trở nên lớn hơn khi lỗi lượng tử hóa (độ phân giải AD và phạm vi đo) càng lớn và thời gian lấy mẫu (tốc độ) càng ngắn.

Chọn thời gian lấy mẫu hợp lý

Độ nhiễu tăng lên và chất lượng kết quả giảm xuống khi tốc độ lấy mẫu tăng lên. Do đó, cần phải chọn thời gian lấy mẫu hợp lý. Thời gian lấy mẫu phải (a) đủ dài để giữ nhiễu ở mức đủ thấp và (b) đủ ngắn để đảm bảo lấy mẫu các biên với độ phân giải đủ.

Một giải pháp cân bằng tốt là chọn thời gian lấy mẫu tạo ra khoảng 3 phân đoạn đo lường (4 mẫu) trong một biên. Ví dụ, tốc độ lấy mẫu phải là khoảng 8ns cho thời gian biên 32ns (80%/20%).

Hình 10 minh họa điều này. Khoảng thời gian giữa các con trỏ tương ứng với 8ns và do đó bằng với thời gian lấy mẫu hợp lý. Ba phần khác nhau được đo trong biên. Biên được lấy mẫu đủ tốt. Đây là sự cân bằng tốt giữa thời gian lấy mẫu và nhiễu và tạo ra tỷ lệ tín hiệu trên nhiễu tốt.

Hình 10. Chiều dài biên so với thời gian lấy mẫu (Ảnh st)

Ch1 = Điện áp pha

Độ chính xác, hạn chế

Tất nhiên, phương pháp này có những hạn chế của nó. Độ dốc của biên được tính toán luôn là giá trị trung bình giữa hai điểm đo. Nếu có một phần dốc hơn giữa các điểm này, nó sẽ không được phát hiện. Tuy nhiên, các thí nghiệm đã chỉ ra rằng có thể đạt được kết quả tốt cho đánh giá thực tế, không khoa học. Phương pháp này ít phù hợp hơn với các yêu cầu khoa học trong đó ngay cả các phần nhỏ nhất của một biên cũng phải đánh giá. Trong trường hợp này, phải lấy mẫu mọi biên riêng lẻ với tốc độ lấy mẫu tối đa có thể và đánh giá một cách khó khăn trong miền thời gian.

Người ta đã chứng minh rằng việc hình thành đạo hàm của điện áp pha là một cách nhanh chóng, đơn giản và thiết thực để đánh giá độ dốc biên trong truyền động động cơ. Điều quan trọng là phải chọn tốc độ lấy mẫu hợp lý, độ phân giải dọc tốt và phạm vi đo nhỏ nhất có thể.

Biên dịch: Phạm Gia Đại

Theo “eepower”, tháng 4/2025